Ya está listo el primer sistema en chip (SoC, por sus siglas en inglés) desarrollado por el consorcio finlandés SoC Hub. Los socios del proyecto se centrarán a continuación en mejorar el diseño, la automatización y el rendimiento del SoC. El primero de los tres chips que desarrollará el consorcio estará en condiciones de implementarse a principios de 2022. El proyecto contribuye a reforzar la soberanía tecnológica de Europa.

Este comunicado de prensa trata sobre multimedia. Ver la noticia completa aquí: https://www.businesswire.com/news/home/20211213005531/es/

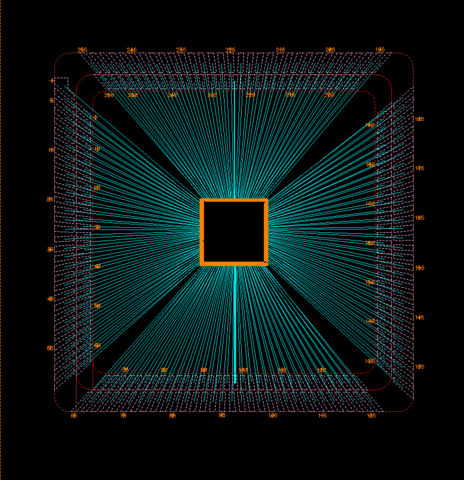

The bonding diagram image shows how the chip IO pads are wired to the package pins. The package is soldered to the printed circuit board. The layout picture depicts how the functional blocks are physically located on the chip. The IO pads that are bonded to the package pins are shown on the sides. Photos: SoC Hub. (Graphic: Business Wire)

El SoC Hub finlandés tiene por objetivo desarrollar el ámbito del diseño de SoC como precursor en Europa y mejorar la posición competitiva de Finlandia. La iniciativa SoC Hub, coordinada por la Universidad de Tampere (Finlandia) y Nokia, se puso en marcha el año pasado. Las actividades de creación conjunta llevadas a cabo por los socios van mucho más allá del alcance de un proyecto de investigación convencional.

«Para desarrollar el SoC se han utilizado los mismos métodos que se emplean en la producción industrial, como el diseño para la comprobabilidad, la verificación exhaustiva y el enfoque en la integración a nivel de sistema en lugar de módulos individuales», afirma Ari Kulmala, profesor de prácticas de Diseño de SoC en la Universidad de Tampere.

Según Kulmala, el chip también puede ser sometido a pruebas por agentes externos, ya que incluye un kit de desarrollo, y puede integrarse en una amplia gama de sistemas.

Uno de los principales objetivos del proyecto SoC Hub es permitir la creación rápida de prototipos para nuevas ideas, por ejemplo, en Internet de las cosas (IoT), aprendizaje automático y tecnologías 5G y 6G en silicio.

El nuevo chip Ballast listo para su fabricación es el primero de una serie de tres chips. Es un chip que será fabricado por TSMC, el mayor fabricante de chips semiconductores del mundo.

Para su fabricación se ha utilizado el flamante proceso de 22 nm Ultra Low Leakage de TSMC, especialmente adecuado para dispositivos IoT y Edge. Ballast contiene varios núcleos de CPU RISC-V, un procesador de señales digitales, un acelerador de inteligencia artificial, numerosas interfaces de tipo sensor y una interfaz de extensión para FPGA. También se ha implementado una pila de software completa, que incluye controladores, herramientas de desarrollo de software y soporte de depuración del chip. El chip admite al mismo tiempo sistemas operativos en tiempo real y Linux.

«Ha sido un placer trabajar con el equipo de SoC Hub. Han sido muy rápidos en el desarrollo del chip, y la calidad del trabajo ha sido sobresaliente», señala Bas Dorren, director de desarrollo comercial de imec.IC-link, que forma parte de imec (un centro de I+D para tecnologías nano y digitales).

En dos años habrá otros dos chips listos para su fabricación

Teniendo en cuenta su gran tamaño, el chip se creó en muy poco tiempo. Es un objetivo ambicioso que se logró gracias al buen espíritu de equipo y a la pericia y experiencia de los especialistas implicados.

«Se ha trabajado mucho para lograr una colaboración fluida entre la Universidad y los socios de la empresa. Varios investigadores noveles han participado en el diseño de Ballast y, por consiguiente, han tenido la oportunidad de aplicar los conocimientos adquiridos en sus estudios en un proyecto industrial», explica Timo Hämäläinen, jefe de la Unidad de Ciencias Informáticas de la Universidad de Tampere.

Además del desarrollo del SoC, la primera fase del proyecto fue también una gran tarea, que implicó la creación del consorcio y la preparación de los acuerdos de software y licencia necesarios. Encabezado por la Universidad de Tampere y Nokia, el consorcio está formado por CoreHW, VLSI Solution, Siru Innovations, TTTEch Flexibilis, Procemex, Wapice y Cargotec como socios.

En el proyecto, financiado por Business Finland, se lanzarán tres SoC para finales de 2023. Las aplicaciones de los chips se planificarán junto con el consorcio del proyecto.

«En las próximas fases del proyecto, podremos centrarnos aún más en la sistemática, la automatización y el rendimiento de los SoC. A pesar de haber alcanzado nuestro primer objetivo, seguiremos adelante sin demora. Es ahora cuando hay que invertir en el desarrollo de SoCs, no mañana», subraya Timo Hämäläinen.

Universidad de Tampere

La Universidad de Tampere, de carácter multidisciplinar, es la segunda universidad más grande de Finlandia. Las puntas de lanza de nuestra investigación y enseñanza son la tecnología, la salud y la sociedad. La Universidad se compromete a abordar los mayores retos a los que se enfrenta la sociedad y a crear nuevas oportunidades. Casi todos los campos de estudio reconocidos a nivel internacional están representados en la Universidad. En conjunto, la Universidad de Tampere y la Universidad de Ciencias Aplicadas de Tampere conforman la comunidad universitaria de Tampere, compuesta por más de 30 000 estudiantes y unos 5000 empleados. www.tuni.fi/en

El texto original en el idioma fuente de este comunicado es la versión oficial autorizada. Las traducciones solo se suministran como adaptación y deben cotejarse con el texto en el idioma fuente, que es la única versión del texto que tendrá un efecto legal.

Vea la versión original en businesswire.com: https://www.businesswire.com/news/home/20211213005531/es/